中心本科生褚衍博主导的时间-数码转换器电路设计工作成果被JINST接收

清华工物系 清华工物系 2025-06-10 19:30 发表于北京

近日,由高能物理中心本科生褚衍博主导的研究成果“A two-stage time-stretching TDC with discrete components”被期刊Journal of Instrumentation接收(文章预印版链接:https://arxiv.org/abs/2505.07514 )。

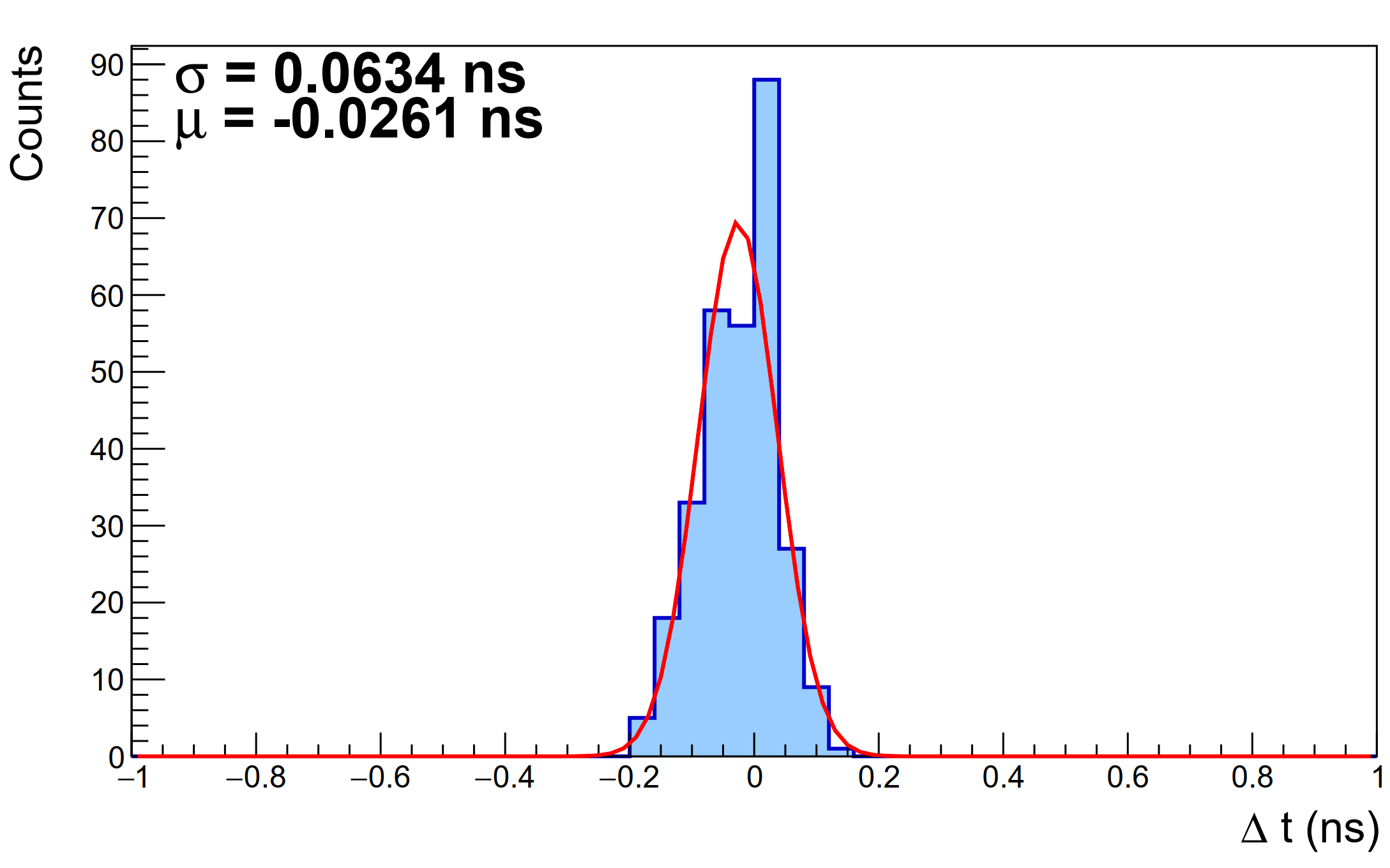

针对未来强子对撞机上的4D像素探测器要求的单像素50ps级时间分辨率、1uW级功耗、100kHz级事例率的极限性能要求,目前尚无满足要求时间-数码转换器(TDC)。本工作提出利用电容充放电的时间放大原理设计了一款TDC原型,该方法可以通过时间放大避免对高速计数时钟的依赖来大幅降低功耗。针对该原理的死时间长的劣势,本工作创造性提出了多级时间放大的思路,最终通过分立元器件实现了针对10ns以内的被测时间量程死时间少于300ns,且同时满足高时间分辨率性能(实测时间分辨率在50-100ps)和低功耗潜能(只使用了100MHz计数时钟)。后期将该电路集成到芯片后有望进一步提高时间分辨率(小于50ps)和实现1uW的功耗目标。

本文第一作者为褚衍博,本工作为褚衍博本科毕业设计工作的主要内容(指导教师为张志财)。该研究得到了清华大学自主科研计划(笃实专项)的支持。

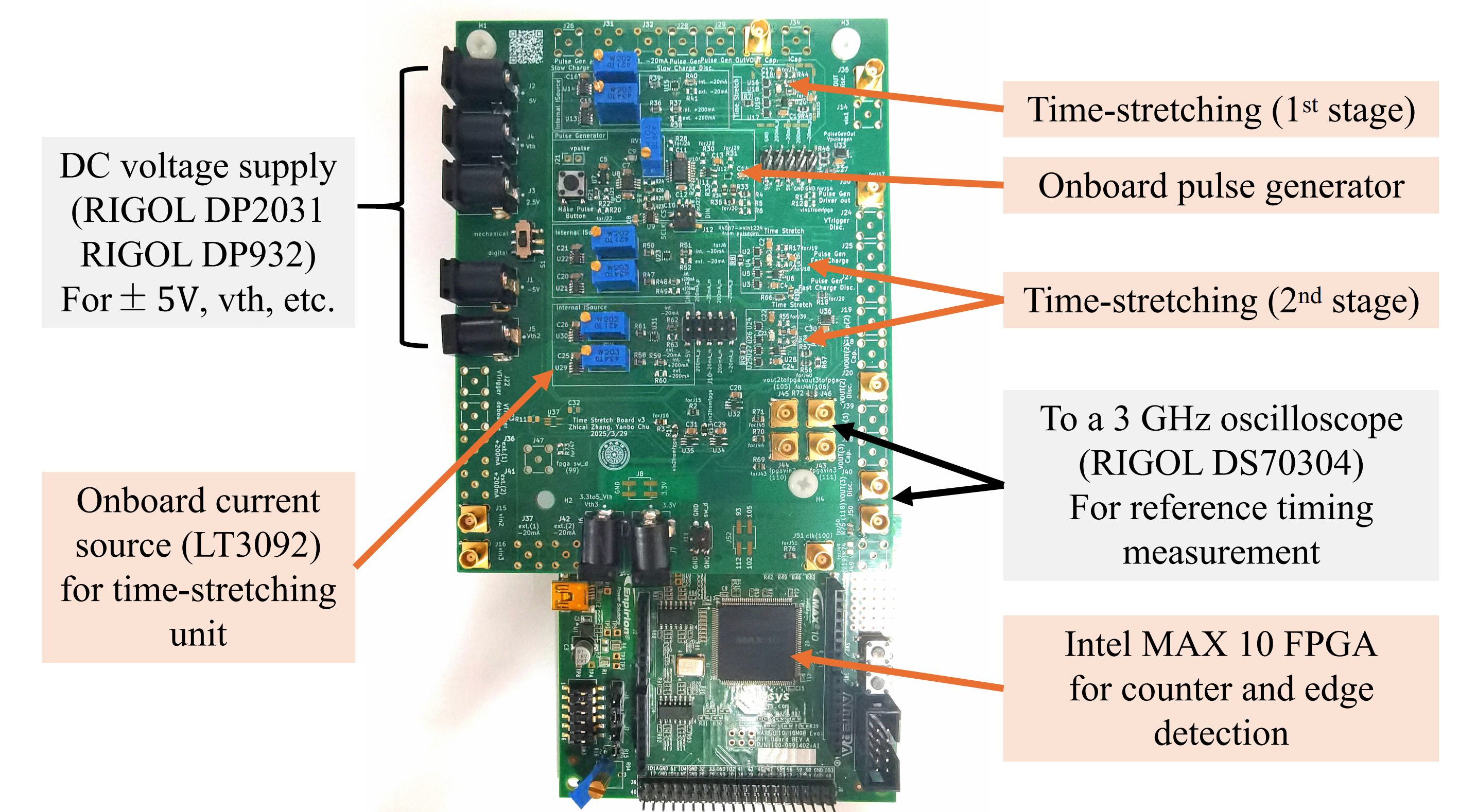

图1:电路实物图和功能示意。

图2:实测时间分辨率(图中显示测量时间和真实时间的差值的分布)。